“Design-for-Testability (DFT) is a critical element in the design of modern, high-performance digital systems.” – Jacob A. Abramovici, electrical engineer and computer scientist, and author of the book Digital Systems Testing and Testable Design.

“The cheapest, fastest, and most reliable components are those that aren’t there” – Dr. V.Nithish Kumar, Associate Professor Grade I, Vellore Institute of Technology, Vellore.

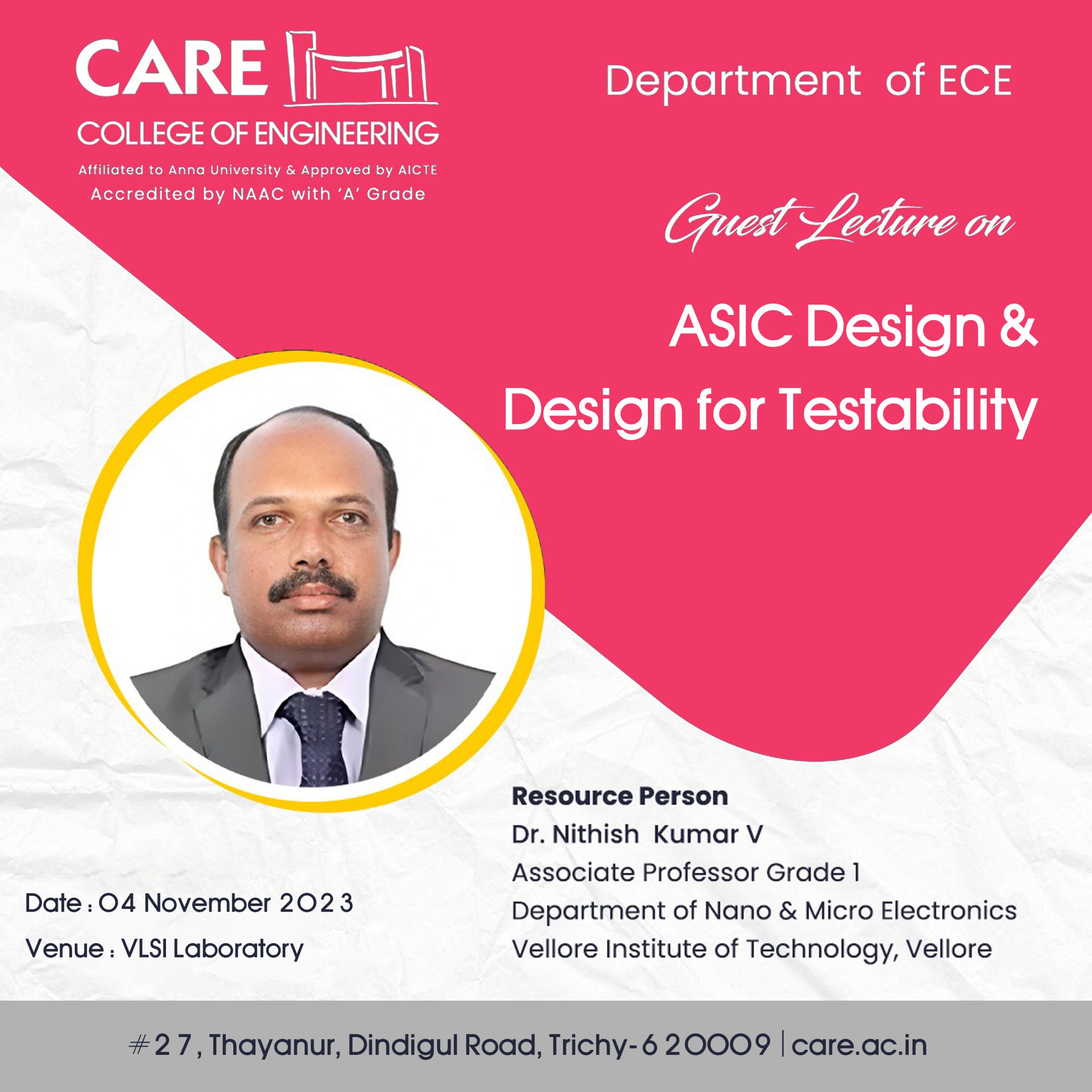

Department of Electronics and Communication Engineering organized a guest lecture “ASIC Design & Design for Testability” on 04th November, 2023. The guest lecture was given by a well-known expert in the field Dr.V.Nithishkumar, Associate Professor Grade I, Vellore Institute of Technology, Vellore. The lecture covered various topics related ASIC Design Flow and to designing chips for easy testing, including Design for Test (DFT), Scan chains, Built-In Self-Test (BIST), and other related techniques.

The lecture began with a comprehensive overview of ASIC design, emphasizing its significance in modern electronics. Dr.V.Nithishkumar explained the fundamental concepts behind ASICs, their applications, and the advantages they offer over other integrated circuit solutions. The guest speaker delved into the ASIC design flow, outlining the key steps involved in taking a concept to a fully functional ASIC. This included specification, design entry, simulation, synthesis, and layout. The resource person provided real-world examples to illustrate each stage of the process, making it more relatable for the students. Dr.V.Nithishkumar discussed the challenges encountered in ASIC design, such as power consumption, area constraints, and performance optimization. The speaker shared insights into how these challenges are addressed in the industry, drawing from their own experiences.

A significant portion of the lecture was dedicated to Design for Testability. The resource person explained the importance of DFT in ensuring the manufacturability and reliability of ASICs. Topics covered included scan chains, test points, and other DFT techniques aimed at simplifying the testing process. To provide a practical understanding of the concepts discussed, The resource person presented case studies of actual ASIC design projects. These case studies allowed students to see how theoretical concepts are applied in real-world scenarios, reinforcing the relevance of the lecture content.

The guest lecture featured an interactive Q&A session, allowing students to pose questions and seek clarification on various aspects of ASIC design and testability. The resource person addressed each query with patience, offering valuable insights and sharing anecdotes from their professional journey.

The guest lecture on ASIC Design and Design for Testability proved to be a valuable addition to our curriculum. Dr.V.Nithishkumar provided a comprehensive overview of ASIC design, shared practical insights, and emphasized the importance of considering testability throughout the design process. This session not only enhanced our understanding of ASIC technology but also inspired us to explore further in this dynamic field. We extend our sincere gratitude to Dr.V.Nithishkumar for sharing their expertise and making this guest lecture a truly enriching experience